In the domain of advanced semiconductor packaging, the transition to Land

Grid Array (LGA) packages presents distinct challenges for IC handling,

transportation, and surface-mount assembly. Unlike leaded devices, LGA packages

rely on planar gold-plated pads that demand absolute protection from physical

contaminants and electrostatic discharge (ESD). The industry-standard solution

for bulk processing, testing, and automated placement is the LGA JEDEC

matrix IC trays. These precision-engineered carriers are not mere

shipping containers; they are integral to yield management, process automation,

and component reliability. This technical analysis, drawing on two decades of

semiconductor supply chain expertise, dissects the architecture, materials, and

application protocols governing JEDEC matrix trays specifically for LGA form

factors.

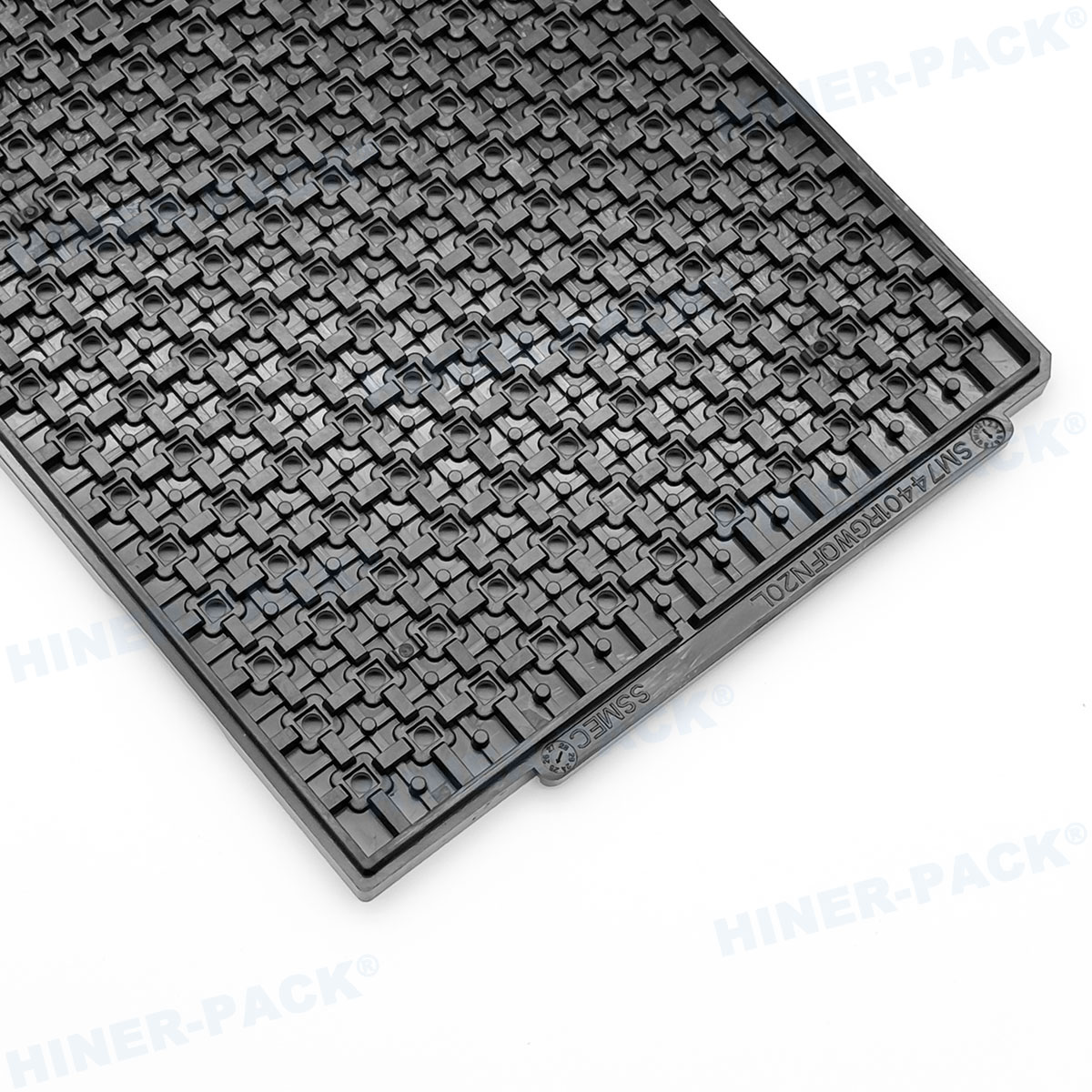

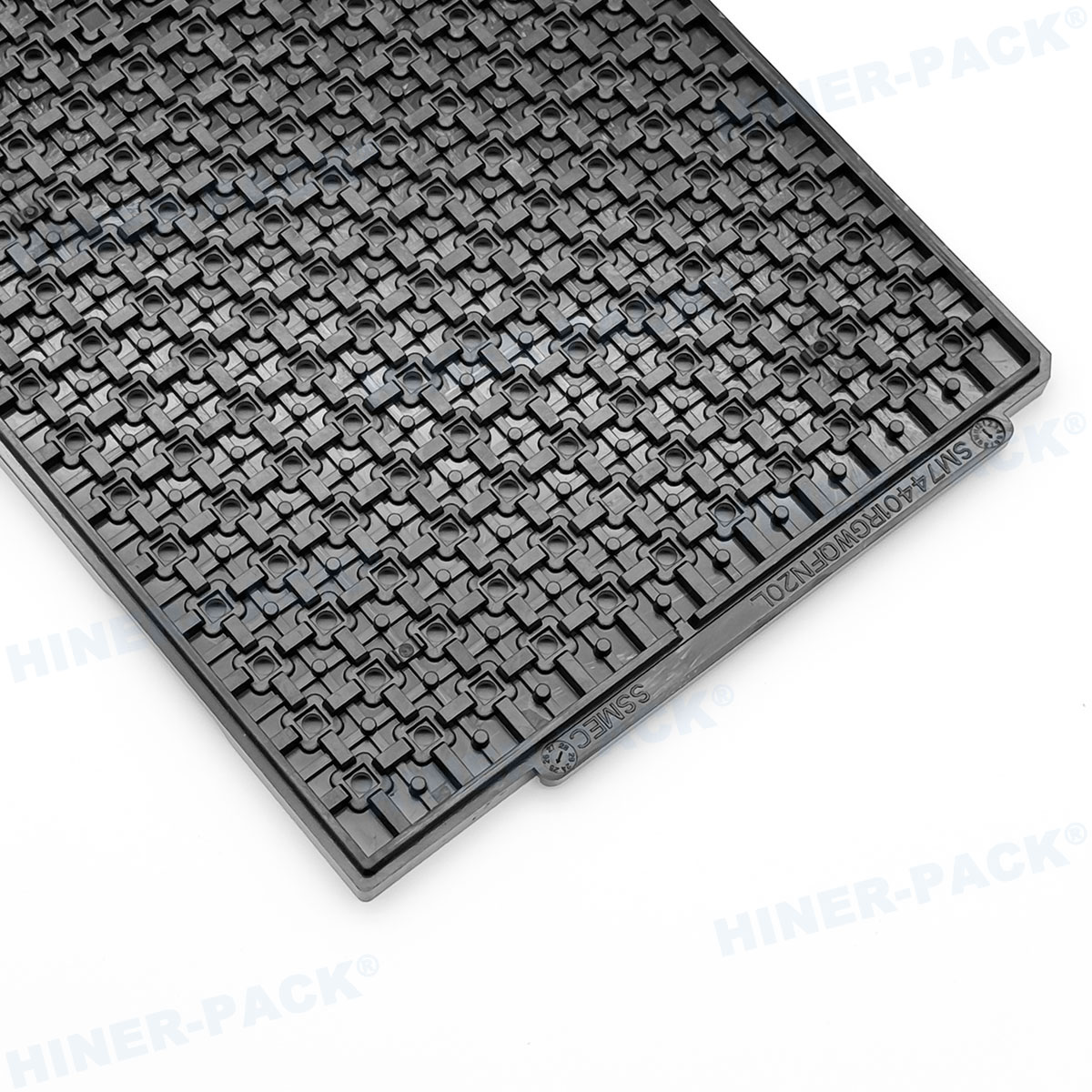

1. Decoding the LGA JEDEC

matrix IC trays Standard: Dimensions, Cell Geometry, and Tray

Stacking

JEDEC Solid State Technology Association established the publication 95

(Design Standard for Trays for Handling and Shipping) to ensure interoperability

across IC manufacturers, test houses, and assembly lines. LGA JEDEC

matrix IC trays conform to specific tray outlines such as 322 mm x

322 mm (JEDEC standard outline for large matrices) or mini trays of 196 mm x 245

mm. The matrix cell array (commonly 4×24, 6×20, or 8×28) is engineered to match

the body size of LGA packages, ranging from 10×10 mm to 50×50 mm for

high-performance computing devices.

Key geometric characteristics include:

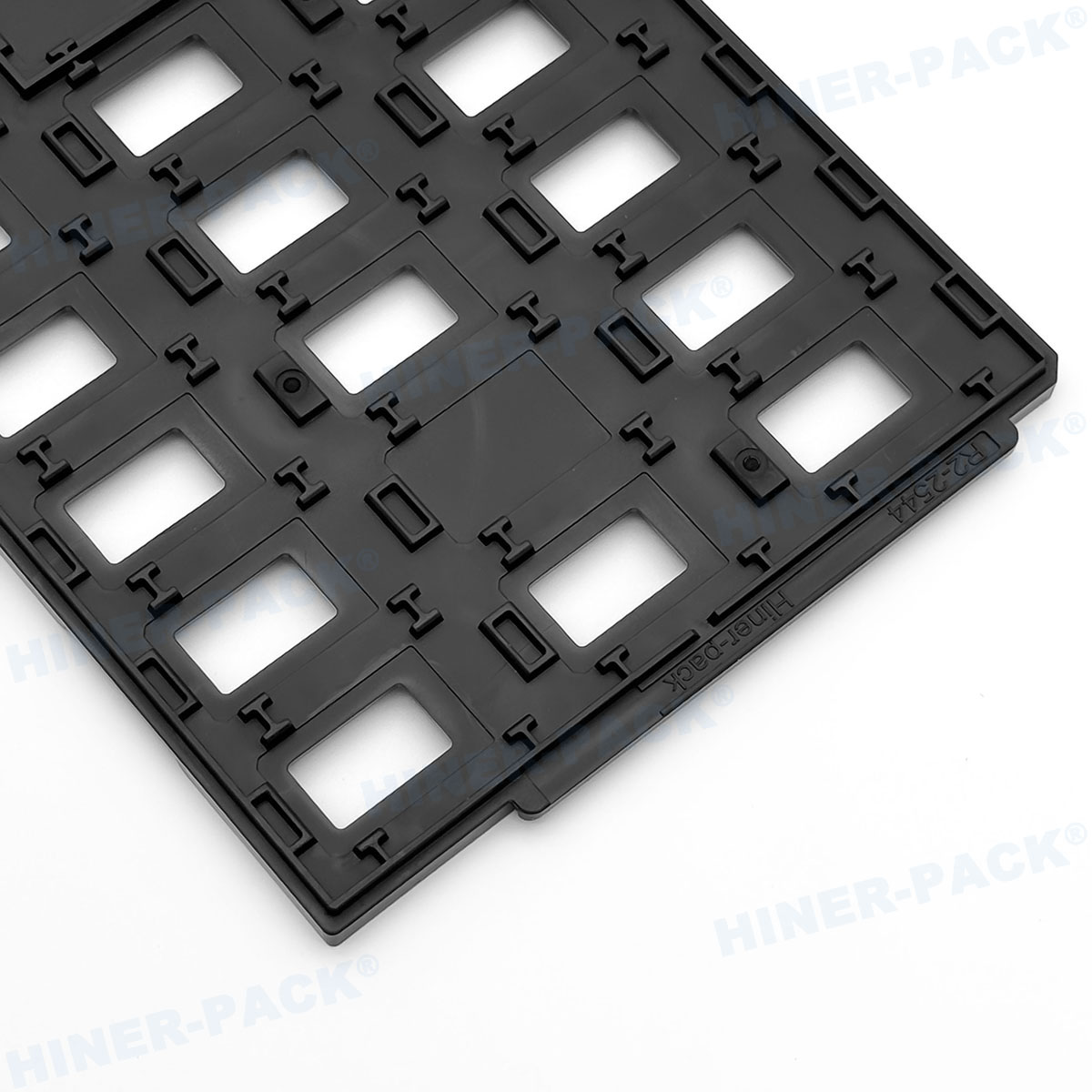

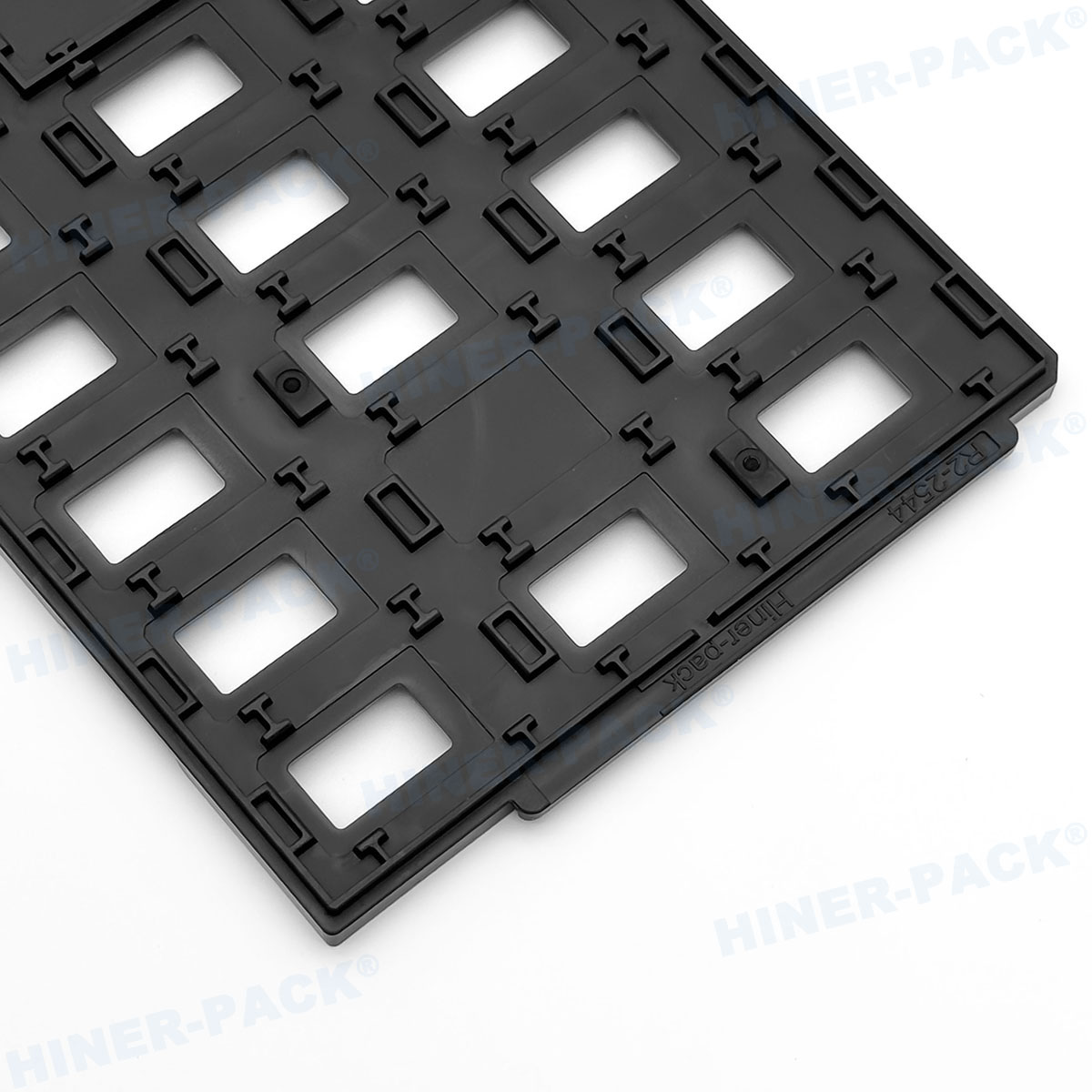

Cell pocket depth and draft angle: Designed to accommodate

LGA package thickness (generally 0.8 mm to 3.5 mm) while providing a

self-centering lead-free pocket.

Orientation features: Chamfered corner indicators and

polarity notches that prevent misplacement in automated pick-and-place

systems.

Stacking ribs and anti-nesting steps: Ensure stable

stacking up to 25 trays without crushing underlying devices or inducing warp on

LGA pad planarity.

Dimensional tolerance: ±0.05 mm for cell pitch and pocket

depth to maintain coplanarity of LGA contacts – critical for avoiding reflow

defects.

The matrix structure allows for maximum density (up to 540 units per tray),

drastically reducing handling costs and floor space in IC burn-in and

calibration stages.

2. Material Science and ESD Performance: Selecting Substrates for Static-Dissipative IC

Packaging

LGA packages are highly susceptible to latent ESD damage because their

contact pads are exposed and leadless. LGA JEDEC

matrix IC trays must therefore provide controlled conductivity. The

most widely adopted materials include:

Polyetherimide (PEI) with carbon-based additives: Offers a

surface resistance range of 10³ to 10⁹ Ω/sq, high thermal stability (continuous

use up to 170°C), and excellent chemical resistance to cleaning agents.

High-temperature Polyphenylene Sulfide (PPS): Suitable for

post-mold curing processes (up to 200°C) and reflow-compatible tray

applications.

Conductive Polycarbonate (PC) blends: Cost-effective for

room temperature testing and logistics, but limited to ≤125°C

applications.

Beyond static dissipation, the material must exhibit low outgassing (to

prevent contamination of gold LGA pads) and consistent dimensional stability

over humidity cycles. Hiner-pack provides

fully characterized JEDEC trays with certified surface resistivity and maximum

warpage ≤0.5 mm across the tray diagonal – a performance metric validated by

optical measurement systems.

3. Critical Application Workflows Using JEDEC Matrix Trays for LGA

Devices

3.1 IC Final Test and Burn-In

During high-temperature burn-in (typically 125°C to 150°C for 48 hours), the

tray must withstand thermal cycling without losing flatness. Matrix trays

designed with reinforced ribs and heat-stabilized polymers ensure contactors

align properly with LGA pads. Hiner-pack offers

custom-machined tray inserts that accommodate different LGA package heights

while preserving cell-to-cell isolation.

3.2 Automated Optical Inspection (AOI) and Tape & Reel Prep

In high-speed IC handling lines, vacuum pickup

compatibility is paramount. JEDEC matrix trays provide clear cell

access with optimized pocket depth so that vacuum nozzles do not contact tray

walls. This reduces nozzle wear by 30% and prevents skipped parts during

pick-and-place.

3.3 In-Plant Logistics for SMT Assembly

Large EMS providers frequently integrate LGA trays directly into

JEDEC-standard tray loaders or auto tray magazines. The tray’s stack alignment

features (corner stops and side rail recesses) enable seamless feeding to

placement machines like Siemens SIPLACE or Fuji NXT, reducing changeover

time.

4. Industry Pain Points and Engineered Solutions for LGA Tray Handling

Despite rigorous standards, four persistent challenges affect yields in LGA

packaging lines:

Warpage-induced contact coplanarity failure: When trays

warp beyond 0.8 mm, LGA pads may tilt during SMT solder paste printing, causing

open joints. The solution is a flatness-verified tray

with peripheral stiffening bridges and edge clips.

Tray-to-tray cell misalignment in stackers: Stack

misalignment leads to device chipping at edges. Precision-molded stacking pins

with ±0.025 mm positioning eliminate this risk.

Triboelectric charging during tray sliding: High-speed

conveyor friction can generate surface charges exceeding 2 kV. Using dissipative

materials (surface resistivity 10⁶–10⁹ Ω) with anti-static additives neutralizes

charges.

Contamination from recycled trays: Reusing trays without

proper cleaning introduces particles >0.5 µm on LGA pads. Hiner-pack implements a

closed-loop cleaning and static verification service, ensuring returned trays

meet ISO Class 5 cleanliness standards.

By addressing these pain points with design optimization and material

upgrades, the industry has reduced LGA field failure rates by nearly 40% when

using qualified matrix trays.

5. Engineering Selection Guide: Specifying LGA JEDEC

matrix IC trays for Production Lines

When procuring trays for LGA-based modules, engineers must evaluate the

following parameters:

Tray outline compatibility: Identify JEDEC Outline Code

(e.g., Tray-4-2416 or T-322-25) matching existing handlers.

Matrix pitch vs LGA body size: Cell X/Y pitch = LGA length

+ 0.5~1.0 mm (clearance for thermal expansion).

Temperature profile: For inline processing, select trays

rated for 5 full cycles of –40°C to +150°C with less than 0.3% irreversible

shrinkage.

ESD classification: Per ANSI/ESD S20.20, require trays with

static-dissipative properties (1×10⁵ to 1×10¹² Ω).

Tray stackability and ID marking: 2D barcode cavities for

automated scanning and traceability from wafer sort to board assembly.

Hiner-pack provides a parametric search tool for JEDEC tray dimensions and material

datasheets, ensuring that each LGA JEDEC

matrix IC trays matches the automated handling environment without

modification.

6. Operational Best Practices: Storage, Cleaning, and Tray Lifecycle

Management

To maximize the utility of matrix trays across thousands of production

cycles, follow these protocols:

Storage conditions: Keep trays in original shipping bags

(ESD shielding) at 20°C–25°C, 40–60% RH. Avoid UV exposure which degrades

dissipative additives.

Cleaning method: Use deionized water with mild surfactant

in ultrasonic baths (max 5 min) followed by forced hot air drying (≤70°C). Never

use abrasive brushes on cell cavities.

Inspection frequency: Visually inspect each tray after 50

cycles; measure flatness using a dial gauge; replace trays if warpage exceeds

0.7 mm or damaged cells found.

Recycling programs: Partner with suppliers offering

take-back schemes to grind and remold trays, reducing plastic waste by 85% and

meeting Scope 3 sustainability goals.

7. Frequently Asked Questions (Technical & Operational)

Q1: What differentiates an LGA JEDEC matrix IC tray from standard IC trays

for QFP or BGA packages?

A1: LGA packages have a flat bottom array of pads without

leads or solder balls, demanding a cell pocket with no sharp ribs that could

scratch gold pads. JEDEC trays for LGA incorporate a smooth, beveled floor and

tighter coplanarity control (max cell depth variation ≤0.05 mm). Additionally,

LGA trays often include anti-tilt features for vacuum pickup, as pad surfaces

offer less friction than solder balls.

Q2: Can JEDEC matrix trays withstand lead-free reflow temperatures if passed

through a vapor phase oven?

A2: Standard trays are not designed for reflow ovens (peak

>245°C). For in-process reflow applications, specialized high-temperature

trays made of PPS (max 270°C) or PEI (max 230°C continuous) are available.

However, most LGA LGA JEDEC

matrix IC trays are intended for ambient temperature handling and

burn-in (<150°C). Do not expose standard trays to reflow.

Q3: How do I verify if a tray complies with JEDEC standard MS-xxx?

A3: Check the tray body for stamped JEDEC code (e.g.,

MS-139, MS-153) and request a compliance certificate from the manufacturer. Key

metrics include pocket pitch tolerance (±0.05 mm), tray outline dimension, stack

height at 25 trays (≤60 mm), and material identification per the JEDEC JEP95

guideline.

Q4: What is the typical cost per unit for high-volume orders of custom LGA

JEDEC trays?

A4: For volumes exceeding 50,000 pieces, custom-engineered

trays range from $1.80 to $4.50 per unit, depending on material (PPS vs. PC) and

matrix density. Standard catalog trays are 30–40% more economical. Hiner-pack provides

volume pricing and engineering consultation for dedicated LGA tray designs.

Q5: How many cycles can a typical LGA Jedec matrix IC tray withstand before

performance degrades?

A5: Under recommended handling conditions (ESD-safe, no

chemical exposure, flat stacking), PC-based trays achieve 300–500 cycles. PPS

and PEI trays often exceed 1,500 cycles. Cyclic degradation manifests as

increased surface resistivity (above 10¹² Ω) or warpage. Regular testing with a

surface resistance meter ensures reliability.

8. Future Outlook: Automation and Traceability in Matrix Tray

Ecosystems

The next generation of LGA JEDEC

matrix IC trays will integrate embedded RFID or conductive trace

patterns for real-time inventory tracking and process control. Smart trays will

communicate with automated guided vehicles (AGVs) to log environmental stress

(humidity shocks, excessive stack pressure) and trigger quality alerts. This

aligns with Industry 4.0 demands for zero-defect logistics. Early adopters

already leverage tray-level data matrix

codes that store batch-specific moisture sensitivity level (MSL)

ratings, directly feeding into SMT line software to adjust bake-out

protocols.

As LGA packaging expands into automotive ADAS and high-performance computing,

the mechanical integrity of JEDEC trays becomes inseparable from functional

safety (ISO 26262). Suppliers must provide full material declarations and

reliability test reports. Hiner-pack supports

these requirements with PPAP level 3 documentation and 100% dimensional

inspection on all tray shipments.

Ready to Optimize Your LGA Handling Line? Request Technical Consultation or

Free Samples

Choosing the correct JEDEC matrix tray reduces device damage, boosts

throughput, and lowers operating costs. Whether you need a standard

off-the-shelf tray or a custom-engineered matrix for a new LGA design, our

engineering team provides full lifecycle support. Contact Hiner-pack today for a

detailed quote, free of charge flatness verification, or to speak directly with

a semiconductor logistics specialist.

Send your inquiry including LGA body size, desired matrix dimensions,

temperature requirements, and annual volume to our sales team. We will respond

within 24 hours with datasheets and commercial proposal.

Request a Quote Now – Hiner-pack Official Website